#### **Features and Benefits**

- Chopper stabilization

- Low switchpoint drift over operating temperature range

- Low sensitivity to stress

- Field programmable for optimized switchpoints

- On-chip protection

- Supply transient protection

- Reverse-battery protection

- On-board voltage regulator

- 3.5 to 24 V operation

Packages: 3 pin SOT23W (suffix LH), and 3 pin SIP (suffix UA)

## **Description**

The A1185 and A1186 are ultrasensitive, two-wire, unipolar Hall effect switches. The operate point,  $B_{OP}$ , can be field-programmed, after final packaging of the sensor and placement into the application. This advanced feature allows the optimization of the sensor switching performance, by effectively accounting for variations caused by mounting tolerances for the device and the target magnet.

This family of devices are produced on the Allegro MicroSystems new DABIC5 BiCMOS wafer fabrication process, which implements a patented, high-frequency, chopper-stabilization technique that achieves magnetic stability and eliminates the offsets that are inherent in single-element devices exposed to harsh application environments. Commonly found in a number of automotive applications, the A1185 and A1186 devices are utilized to sense: seat track position, seat belt buckle presence, hood/trunk latching, and shift selector position.

Two-wire unipolar switches are particularly advantageous in price-sensitive applications, because they require one less wire than the more traditional open-collector output switches.

Continued on the next page...

Not to scale

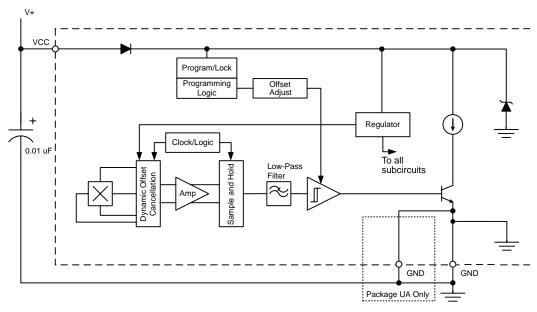

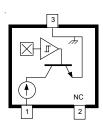

## **Functional Block Diagram**

# A1185 and A1186

# Ultrasensitive Two-Wire Field-Programmable Chopper-Stabilized Unipolar Hall Effect Switches

#### **Description (continued)**

Additionally, the system designer gains inherent diagnostics because output current normally flows in either of two narrowly-specified ranges. This provides distinct current ranges for  $I_{OUT(H)}$  and  $I_{OUT(L)}$ . Any output current level outside of these two ranges is a fault condition.

Other features of the A1185 and A1186 devices include on-chip transient protection and a Zener clamp on the power supply to protect against overvoltage conditions on the supply line.

The output current of the A1186 switches HIGH in the presence of a south polarity magnetic field of sufficient strength; and switches LOW otherwise, including when there is no significant magnetic field

present. The A1185 has an inverted output current level: switching Low in the presence of a south polarity magnetic field of sufficient strength, and HIGH otherwise.

Both devices are offered in two package styles: LH, a SOT-23W miniature low-profile package for surface-mount applications, and UA, a three-lead ultramini Single Inline Package (SIP) for throughhole mounting. Each package is available in a lead (Pb) free version (suffix, –*T*) with 100% matte tin plated leadframe.

Factory-programmed versions are also available. Refer to: A1145 and A1146.

## **Selection Guide**

| Part Number  | Packing <sup>1</sup>         | Mounting         | Ambient, T <sub>A</sub><br>(°C) | Output<br>South (+) Field <sup>2</sup> | Supply Current at Low<br>Output, I <sub>CC(L)</sub><br>(mA) |  |

|--------------|------------------------------|------------------|---------------------------------|----------------------------------------|-------------------------------------------------------------|--|

| A1185ELHLT-T | 7-in. reel, 3000 pieces/reel | Surface mount    | -40 to 85                       |                                        |                                                             |  |

| A1185EUA-T   | Bulk, 500 pieces/bag         | SIP through hole | <del>-4</del> 0 to 85           | Law                                    |                                                             |  |

| A1185LLHLT-T | 7-in. reel, 3000 pieces/reel | Surface mount    | 40 +- 450                       | Low                                    |                                                             |  |

| A1185LUA-T   | Bulk, 500 pieces/bag         | SIP through hole | -40 to 150                      |                                        | 54.00                                                       |  |

| A1186ELHLT-T | 7-in. reel, 3000 pieces/reel | Surface mount    | 40 4- 05                        | -40 to 85                              | 5 to 6.9                                                    |  |

| A1186EUA-T   | Bulk, 500 pieces/bag         | SIP through hole | <del>-4</del> 0 t0 85           |                                        |                                                             |  |

| A1186LLHLT-T | 7-in. reel, 3000 pieces/reel | Surface mount    | 40 to 450                       |                                        |                                                             |  |

| A1186LUA-T   | Bulk, 500 pieces/bag         | SIP through hole | -40 to 150                      |                                        |                                                             |  |

<sup>&</sup>lt;sup>1</sup>Contact Allegro for additional packing options.

# Pb

### **Absolute Maximum Ratings**

| Characteristic                   | Symbol               | Notes   | Rating     | Units |

|----------------------------------|----------------------|---------|------------|-------|

| Supply Voltage                   | $V_{CC}$             |         | 28         | V     |

| Reverse Supply Voltage           | V <sub>RCC</sub>     |         | <b>–18</b> | V     |

| Magnetic Flux Density            | В                    |         | Unlimited  | G     |

| On anating Ameliant Tanananatura | T <sub>A</sub>       | Range E | -40 to 85  | °C    |

| Operating Ambient Temperature    |                      | Range L | -40 to 150 | °C    |

| Maximum Junction Temperature     | T <sub>J</sub> (max) |         | 165        | °C    |

| Storage Temperature              | T <sub>stg</sub>     |         | -65 to 170 | °C    |

<sup>&</sup>lt;sup>2</sup>South (+) magnetic fields must be of sufficient strength.

# A1185 and A1186

# Ultrasensitive Two-Wire Field-Programmable Chopper-Stabilized Unipolar Hall Effect Switches

#### ELECTRICAL CHARACTERISTICS over the operating voltage and temperature ranges, unless otherwise specified

| Characteristic                          | Symbol               | Test Conditions                                                                         | Min. | Тур. | Max. | Units |

|-----------------------------------------|----------------------|-----------------------------------------------------------------------------------------|------|------|------|-------|

| Supply Voltage <sup>1</sup>             | V <sub>CC</sub>      | Device powered on                                                                       | 3.5  | _    | 24   | V     |

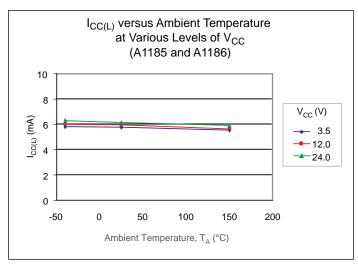

| O                                       | I <sub>CC(L)</sub>   | B >B <sub>OP</sub> for A1185; B <b<sub>RP for A1186</b<sub>                             | 5    | _    | 6.9  | mA    |

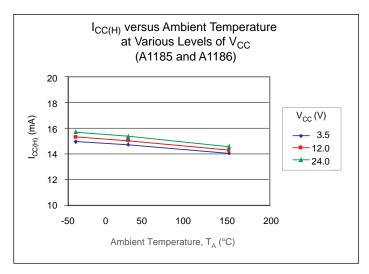

| Supply Current <sup>2</sup>             | I <sub>CC(H)</sub>   | B >B <sub>OP</sub> for A1186; B <b<sub>RP for A1185</b<sub>                             | 12   | _    | 17   | mA    |

| Supply Zener Clamp Voltage              | V <sub>ZSupply</sub> | $I_{CC} = I_{CC(L)(Max)} + 3 \text{ mA}; T_A = 25^{\circ}\text{C}$                      | 28   | _    | 40   | V     |

| Supply Zener Clamp Current <sup>3</sup> | I <sub>ZSupply</sub> | V <sub>Supply</sub> = 28 V                                                              | _    | _    | 9.9  | mA    |

| Reverse Supply Current                  | I <sub>RCC</sub>     | V <sub>RCC</sub> = -18 V                                                                | _    | _    | 1.6  | mA    |

| Output Slew Rate <sup>4</sup>           | di/dt                | No bypass capacitor; capacitance of the oscilloscope performing the measurement = 20 pF | _    | 36   | -    | mΑ/μs |

| Chopping Frequency                      | f <sub>C</sub>       |                                                                                         | _    | 200  | _    | kHz   |

| Power-On Time <sup>5</sup>              | t <sub>on</sub>      | After factory trimming; with and without bypass capacitor ( $C_{BYP} = 0.01 \mu F$ )    | _    | _    | 25   | μs    |

| Power-On State <sup>6,7</sup>           | POS                  | $t_{on} \le t_{on(max)}$ ; $V_{CC}$ slew rate > 25 mV/ $\mu$ s                          | _    | HIGH | _    | _     |

<sup>&</sup>lt;sup>1</sup>V<sub>CC</sub> represents the generated voltage between the VCC pin and the GND pin.

#### MAGNETIC CHARACTERISTICS<sup>1</sup> over the operating voltage and temperature ranges, unless otherwise specified

| Characteristic                       | Symbol               | Test Conditions                                                  | Min. | Тур. | Max. | Units |

|--------------------------------------|----------------------|------------------------------------------------------------------|------|------|------|-------|

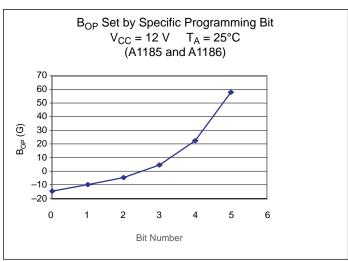

| Programmable Operate Point Range     | B <sub>OPrange</sub> | $I_{CC} = I_{CC(L)}$ for A1185<br>$I_{CC} = I_{CC(H)}$ for A1186 | 10   | _    | 60   | G     |

| Initial Operate Point Range          | B <sub>OPinit</sub>  | V <sub>CC</sub> =12 V                                            | -    | -10  | 10   | G     |

| Switchpoint Step Size <sup>2</sup>   | B <sub>RES</sub>     | V <sub>CC</sub> =5 V, T <sub>A</sub> = 25°C                      | 2    | 4    | 6    | G     |

| Nb. a. of Danasanaira Bita           |                      | Switchpoint setting                                              | _    | 5    | _    | Bit   |

| Number of Programming Bits           | _                    | Programming locking                                              | _    | 1    | _    | Bit   |

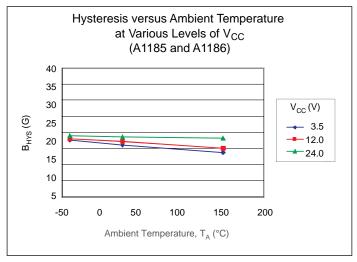

| Temperature Drift of B <sub>OP</sub> | $\Delta B_OP$        |                                                                  | _    | _    | ±20  | G     |

| Hysteresis                           | B <sub>HYS</sub>     | $B_{HYS} = B_{OP} - B_{RP}$                                      | 5    | 15   | 30   | G     |

<sup>&</sup>lt;sup>1</sup>Relative values of B use the algebraic convention, where positive values indicate south magnetic polarity, and negative values indicate north magnetic polarity; therefore greater B values indicate a stronger south polarity field (or a weaker north polarity field, if present).

<sup>&</sup>lt;sup>2</sup>Relative values of B use the algebraic convention, where positive values indicate south magnetic polarity, and negative values indicate north magnetic polarity; therefore greater B values indicate a stronger south polarity field (or a weaker north polarity field, if present).

$<sup>{}^{3}</sup>I_{ZSUPPLY(max)} = I_{CCL(max)} + 3 \text{ mA}.$

<sup>&</sup>lt;sup>4</sup>Measured without bypass capacitor between VCC and GND. Use of a bypass capacitor results in slower current change.

<sup>&</sup>lt;sup>5</sup>Measured with and without bypass capacitor of 0.01 μF. Adding a larger bypass capacitor causes longer Power-On Time.

<sup>&</sup>lt;sup>6</sup>POS is defined as true only with a V<sub>CC</sub> slew rate of 25 mV/μs or greater. Operation with a V<sub>CC</sub> slew rate less than 25 mV/μs can permanently harm device performance.

<sup>&</sup>lt;sup>7</sup>POS is undefined for  $t > t_{on}$  or  $B_{RP} < B < B_{OP}$ .

<sup>&</sup>lt;sup>2</sup>The range of values specified for B<sub>RES</sub> is a maximum, derived from the cumulative programming bit errors.

## Characteristic Data

## Device Qualification Program

Contact Allegro for information.

## EMC (Electromagnetic Compatibility) Requirements

Contact your local representative for EMC results.

| Test Name              | Reference Specification |

|------------------------|-------------------------|

| ESD – Human Body Model | AEC-Q100-002            |

| ESD – Machine Model    | AEC-Q100-003            |

| Conducted Transients   | ISO 7637-2              |

| Direct RF Injection    | ISO 11452-7             |

| Bulk Current Injection | ISO 11452-4             |

| TEM Cell               | ISO 11452-3             |

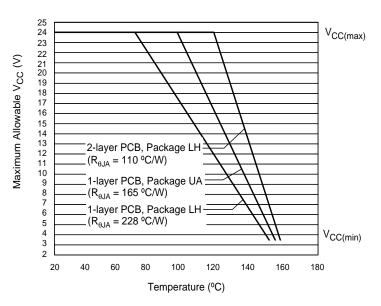

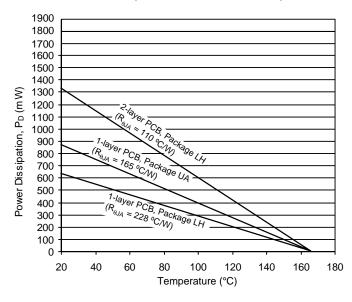

## THERMAL CHARACTERISTICS may require derating at maximum conditions, see application information

| Characteristic Symbol      |                | Test Conditions*                                                                                           |     | Units |

|----------------------------|----------------|------------------------------------------------------------------------------------------------------------|-----|-------|

|                            |                | Package LH, 1-layer PCB with copper limited to solder pads                                                 |     | °C/W  |

| Package Thermal Resistance | $R_{	heta JA}$ | $R_{\theta JA}$ Package LH, 2-layer PCB with 0.463 in.2 of copper area each side connected by thermal vias | 110 | °C/W  |

|                            |                | Package UA, 1-layer PCB with copper limited to solder pads                                                 | 110 | °C/W  |

<sup>\*</sup>Additional thermal information available on Allegro Web site.

## **Power Derating Curve**

#### **Power Dissipation versus Ambient Temperature**

## **Functional Description**

## Operation

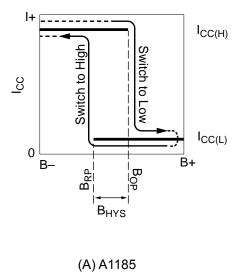

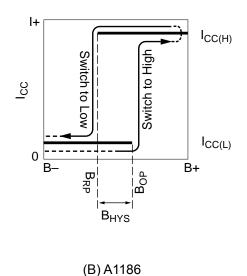

The output,  $I_{CC}$ , of the A1185 switches low after the magnetic field at the Hall sensor exceeds the operate point threshold,  $B_{OP}$ . When the magnetic field is reduced to below the release point threshold,  $B_{RP}$ , the device output goes high. The differences between the magnetic operate and release point is called the

hysteresis of the device,  $B_{HYS}$ . This built-in hysteresis allows clean switching of the output even in the presence of external mechanical vibration and electrical noise. The A1186 device switches with opposite polarity for similar  $B_{OP}$  and  $B_{RP}$  values, in comparison to the A1185 (see figure 1).

Figure 1. Alternative switching behaviors are available in the A118x device family. On the horizontal axis, the B+ direction indicates increasing south polarity magnetic field strength, and the B– direction indicates decreasing south polarity field strength (including the case of increasing north polarity).

## **Chopper Stabilization Technique**

A limiting factor for switchpoint accuracy when using Hall effect technology is the small signal voltage developed across the Hall element. This voltage is proportionally small relative to the offset that can be produced at the output of the Hall sensor device. This makes it difficult to process the signal and maintain an accurate, reliable output over the specified temperature and voltage range.

Chopper stabilization is a unique approach used to minimize Hall offset on the chip. The Allegro patented technique, dynamic quadrature offset cancellation, removes key sources of the output drift induced by temperature and package stress. This offset reduction technique is based on a signal modulation-demodulation process. The undesired offset signal is separated from the magnetically induced signal in the frequency domain through modulation. The subsequent demodulation acts as a modulation process for the offset causing the magnetically induced signal to recover its original spectrum at base band while the dc offset becomes a high frequency signal. Then, using a low-pass filter, the signal passes while the modulated dc offset is suppressed.

The chopper stabilization technique uses a 200 kHz high frequency clock. For demodulation process, a sample-and-hold

technique is used, where the sampling is performed at twice the chopper frequency (400KHz). The sampling demodulation process produces higher accuracy and faster signal processing capability. Using this chopper stabilization approach, the chip is desensitized to the effects of temperature and stress. This technique produces devices that have an extremely stable quiescent Hall output voltage, is immune to thermal stress, and has precise recoverability after temperature cycling. This technique is made possible through the use of a BiCMOS process which allows the use of low-offset and low-noise amplifiers in combination with high-density logic integration and sample-and-hold circuits.

The repeatability of switching with a magnetic field is slightly affected using a chopper technique. The Allegro high frequency chopping approach minimizes the affect of jitter and makes it imperceptible in most applications. Applications that may notice the degradation are those that require the precise sensing of alternating magnetic fields such as ring magnet speed sensing. For those applications, Allegro recommends the "low jitter" family of digital sensors.

Figure 2. Chopper stabilization circuit (dynamic quadrature offset cancellation)

## **Application Information**

For additional general application information, visit the Allegro Web site at www. allegromicro.com.

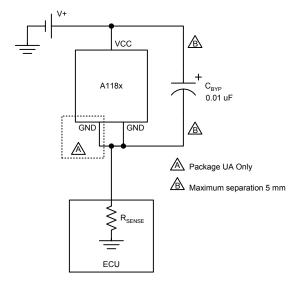

#### Typical Application and Programming Circuit

The A118x family of devices MUST be protected by an external bypass capacitor,  $C_{BYP}$ , connected between the supply pin, VCC, and the ground pin, GND, of the device.  $C_{BYP}$  reduces both external noise and the noise generated by the chopper-stabilization function. As shown in figure 3, a 0.01  $\mu$ F capacitor is typical. (For programming the device, a 0.1  $\mu$ F capacitor is recommended for proper fuse blowing.)

Installation of  $C_{\rm BYP}$  must ensure that the traces that connect it to the A118x pins are no greater than 5 mm in length. (For programming the device, the capacitor may be further away from the device, including mounting on the board used for programming the device.)

C<sub>BYP</sub> serves only to protect the A118x internal circuitry. All high-frequency interferences conducted along the supply lines

are passed directly to the load through  $C_{BYP}$ . As a result, the load ECU (electronic control unit) must have sufficient protection, other than  $C_{BYP}$  installed in parallel with the A118x.

A series resistor on the supply side,  $R_S$  (not shown), in combination with  $C_{\rm BYP}$ , creates a filter for EMI pulses.

When determining the minimum  $V_{CC}$  requirement of the A118x device, the voltage drops across  $R_S$  and the ECU sense resistor,  $R_{SENSE}$ , must be taken into consideration. The typical value for  $R_{SENSE}$  is approximately  $100~\Omega$ . (All programming, including code and lock-bit programming, should be done with direct connections to VCC and GND, with the use of a 0.1 uF bypass capacitor. Programming across the series resistor or sense resistor may not allow enough energy to properly blow the fuses in the device, as required for proper programming. The result would be incorrect switchpoints.

Figure 3. Typical application circuit

## **Power Derating**

The device must be operated below the maximum junction temperature of the device, T<sub>J(max)</sub>. Under certain combinations of peak conditions, reliable operation may require derating supplied power or improving the heat dissipation properties of the application. This section presents a procedure for correlating factors affecting operating T<sub>I</sub>. (Thermal data is also available on the Allegro MicroSystems Web site.)

The Package Thermal Resistance,  $R_{\theta IA}$ , is a figure of merit summarizing the ability of the application and the device to dissipate heat from the junction (die), through all paths to the ambient air. Its primary component is the Effective Thermal Conductivity. K, of the printed circuit board, including adjacent devices and traces. Radiation from the die through the device case, R<sub>0.1C</sub>, is relatively small component of  $R_{\theta JA}$ . Ambient air temperature, T<sub>A</sub>, and air motion are significant external factors, damped by overmolding.

The effect of varying power levels (Power Dissipation, P<sub>D</sub>), can be estimated. The following formulas represent the fundamental relationships used to estimate T<sub>I</sub>, at P<sub>D</sub>.

$$P_D = V_{IN} \times I_{IN} \tag{1}$$

$$\Delta T = P_D \times R_{\theta JA} (2)$$

$$T_{J} = T_{A} + \Delta T \tag{3}$$

For example, given common conditions such as:  $T_A = 25^{\circ}C$ ,  $V_{CC} = 12 \text{ V}$ ,  $I_{CC} = 4 \text{ mA}$ , and  $R_{\theta JA} = 140 \text{ °C/W}$ , then:

$$P_D = V_{CC} \times I_{CC} = 12 \text{ V} \times 4 \text{ mA} = 48 \text{ mW}$$

$$\Delta T = P_D \times R_{\theta IA} = 48 \text{ mW} \times 140 \text{ }^{\circ}\text{C/W} = 7^{\circ}\text{C}$$

$$T_1 = T_{\Lambda} + \Delta T = 25^{\circ}C + 7^{\circ}C = 32^{\circ}C$$

A worst-case estimate,  $P_{D(max)}$ , represents the maximum allowable power level ( $V_{CC(max)}$ ,  $I_{CC(max)}$ ), without exceeding  $T_{J(max)}$ , at a selected  $R_{\theta JA}$  and  $T_A$ .

Example: Reliability for V<sub>CC</sub> at T<sub>A</sub>=150°C, package UA, using minimum-K PCB.

Observe the worst-case ratings for the device, specifically:  $R_{\theta JA} = 165 \text{ °C/W}, T_{J(max)} = 165 \text{ °C}, V_{CC(max)} = 24 \text{ V}, \text{ and}$  $I_{CC(max)} = 17 \text{ mA}.$

Calculate the maximum allowable power level, P<sub>D(max)</sub>. First, invert equation 3:

$$\Delta T_{\text{max}} = T_{\text{J(max)}} - T_{\text{A}} = 165 \,^{\circ}\text{C} - 150 \,^{\circ}\text{C} = 15 \,^{\circ}\text{C}$$

This provides the allowable increase to T<sub>I</sub> resulting from internal power dissipation. Then, invert equation 2:

$$P_{D(max)} = \Delta T_{max} \div R_{\theta JA} = 15^{\circ}C \div 165^{\circ}C/W = 91 \text{ mW}$$

Finally, invert equation 1 with respect to voltage:

$$V_{CC(est)} = P_{D(max)} \div I_{CC(max)} = 91 \text{ mW} \div 17 \text{ mA} = 5 \text{ V}$$

The result indicates that, at T<sub>A</sub>, the application and device can dissipate adequate amounts of heat at voltages  $\leq V_{CC(est)}$ .

Compare  $V_{CC(est)}$  to  $V_{CC(max)}$ . If  $V_{CC(est)} \leq V_{CC(max)}$ , then reliable operation between  $V_{CC(est)}$  and  $V_{CC(max)}$  requires enhanced  $R_{\theta JA}$ . If  $V_{CC(est)} \ge V_{CC(max)}$ , then operation between  $V_{CC(est)}$  and  $V_{CC(max)}$  is reliable under these conditions.

# A1185 and A1186

# Ultrasensitive Two-Wire Field-Programmable Chopper-Stabilized Unipolar Hall Effect Switches

## **Programming Protocol**

The operate switchpoint, B<sub>OP</sub>, can be field-programmed. To do so, a coded series of voltage pulses through the VCC pin is used to set bitfields in onboard registers. The effect on the device output can be monitored, and the registers can be cleared and set repeatedly until the required B<sub>OP</sub> is achieved. To make the setting permanent, bitfield-level solid state fuses are blown, and finally, a device-level fuse is blown, blocking any further coding. It is not necessary to program the release switchpoint, B<sub>RP</sub>, because the difference between B<sub>OP</sub> and B<sub>RP</sub>, referred to as the hysteresis, B<sub>HYS</sub>, is fixed.

The range of values between  $B_{OP(min)}$  and  $B_{OP(max)}$  is scaled to 31 increments. The actual change in magnetic flux (G) represented by each increment is indicated by B<sub>RES</sub> (see the Operating Characteristics table; however, testing is the only method for verifying the resulting B<sub>OP</sub>). For programming, the 31 increments are individually identified using 5 data bits, which are physically represented by 5 bitfields in the onboard registers. By setting these bitfields, the corresponding calibration value is programmed into the device.

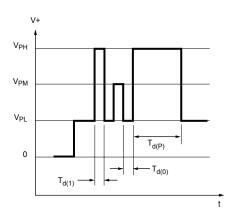

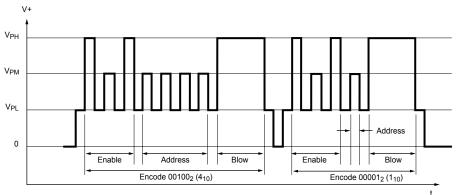

Three voltage levels are used in programming the device: a low voltage, V<sub>PL</sub>, a minimum required to sustain register settings; a mid-level voltage, V<sub>PM</sub>, used to increment the address counter in the device; and a high voltage, V<sub>PH</sub>, used to separate sets of V<sub>PM</sub> pulses (when short in duration) and to blow fuses (when long in duration). A fourth voltage level, essentially 0 V, is used to clear the registers between pulse sequences. The pulse values are shown in the Programming Protocol Characteristics table and in figure 4.

Figure 4. Pulse amplitudes and durations

Additional information on device programming and programming products is available on www. allegromicro.com. Programming hardware is available for purchase, and programming software is available free of charge.

**Code Programming.** Each bitfield must be individually set. To do so, a pulse sequence must be transmitted for each bitfield that is being set to 1. If more than one bitfield is being set to 1, all pulse sequences must be sent, one after the other, without allowing V<sub>CC</sub> to fall to zero (which clears the registers).

The same pulse sequence is used to provisionally set bitfields as is used to permanently set bitfield-level fuses. The only difference is that when provisionally setting bitfields, no fuse-blowing pulse is sent at the end of the pulse sequence.

#### PROGRAMMING PROTOCOL CHARACTERISTICS, over operating temperature range, unless otherwise noted

| Characteristic                   | Symbol            | Test Conditions                                                         | Min. | Тур. | Max. | Units |

|----------------------------------|-------------------|-------------------------------------------------------------------------|------|------|------|-------|

|                                  | V <sub>PL</sub>   | Minimum voltage range during programming                                | 4.5  | 5.0  | 5.5  | V     |

| Programming Voltage <sup>1</sup> | V <sub>PM</sub>   |                                                                         | 11.5 | 12.5 | 13.5 | V     |

|                                  | V <sub>PH</sub>   |                                                                         | 25   | 26   | 27   | V     |

| Programming Current <sup>2</sup> | I <sub>PP</sub>   | $t_r$ = 11 $\mu$ s; 5 V $\rightarrow$ 26 V; $C_{BYP}$ = 0.1 $\mu$ F     | -    | 190  | -    | mA    |

|                                  | t <sub>d(0)</sub> | OFF time between programming bits                                       | 20   | -    | -    | μs    |

| Pulse Width                      | t <sub>d(1)</sub> | Pulse duration for enable and addressing sequences                      | 20   | -    | -    | μs    |

|                                  | t <sub>d(P)</sub> | Pulse duration for fuse blowing                                         | 100  | 300  | -    | μs    |

| Pulse Rise Time                  | t <sub>r</sub>    | V <sub>PL</sub> to V <sub>PM</sub> ; V <sub>PL</sub> to V <sub>PH</sub> | 5    | -    | 20   | μs    |

| Pulse Fall Time                  | t <sub>f</sub>    | V <sub>PM</sub> to V <sub>PL</sub> ; V <sub>PH</sub> to V <sub>PL</sub> | 5    | -    | 100  | μs    |

<sup>&</sup>lt;sup>1</sup>Programming voltages are measured at the VCC pin.

$<sup>^2</sup>$ A bypass capacitor with a minimum capacitance of 0.1  $\mu$ F must be connected from VCC to the GND pin of the A118x device in order to provide the current necessary to blow the fuse.

## A1185 and A1186

# Ultrasensitive Two-Wire Field-Programmable Chopper-Stabilized Unipolar Hall Effect Switches

The pulse sequences consist of the following groups of pulses:

- 1. An enable sequence.

- 2. A bitfield address sequence.

- 3. When permanently setting the bitfield, a long V<sub>PH</sub> fuse-blowing pulse. (Note: Blown bit fuses cannot be reset.)

- 4. When permanently setting the bitfield, the level of  $V_{CC}$  must be allowed to drop to zero between each pulse sequence, in order to clear all registers. However, when provisionally setting bitfields, V<sub>CC</sub> must be maintained at V<sub>PL</sub> between pulse sequences, in order to maintain the prior bitfield settings while preparing to set additional bitfields.

Bitfields that are not set are evaluated as zeros. The bitfield-level fuses for 0 value bitfields are never blown. This prevents inadvertently setting the bitfield to 1. Instead, blowing the devicelevel fuse protects the 0 bitfields from being accidentally set in the future.

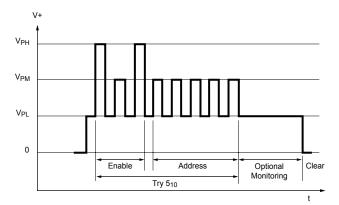

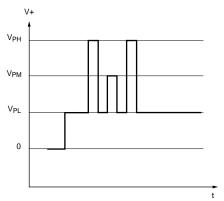

When provisionally trying the calibration value, one pulse sequence is used, using decimal values. The sequence for setting the value  $5_{10}$  is shown in figure 5.

When permanently setting values, the bitfields must be set individually, and 5<sub>10</sub> must be programmed as binary 101. Bit 3 is set to 1  $(000100_2$ , which is  $4_{10}$ ), then bit 1 is set to 1  $(000001_2$ , which is  $1_{10}$ ). Bit 2 is ignored, and so remains 0.Two pulse sequences for permanently setting the calibration value 5 are shown in figure 6. The final V<sub>PH</sub> pulse is maintained for a longer period, enough to blow the corresponding bitfield-level fuse.

Figure 5. Pulse sequence to provisionally try calibration value 5.

Figure 6. Pulse sequence to permanently encode calibration value 5 (101 binary, or bitfield address 3 and bitfield address 1).

**Enabling Addressing Mode**. The first segment of code is a keying sequence used to enable the bitfield addressing mode. As shown in figure 7, this segment consists of one short  $V_{PH}$  pulse, one  $V_{PM}$  pulse, and one short  $V_{PH}$  pulse, with no supply interruptions. This sequence is designed to prevent the device from being programmed accidentally, such as by noise on the supply line

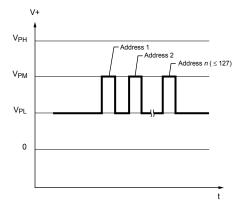

**Address Selection**. After addressing mode is enabled, the target bitfield address, is indicated by a series of  $V_{PM}$  pulses, as shown in figure 8.

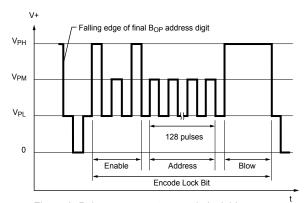

**Lock Bit Programming.** After the desired  $B_{OP}$  calibration value is programmed, and all of the corresponding bitfield-level fuses are blown, the device-level fuse should be blown. To do so, the lock bit (bitfield address 32) should be encoded as 1 and have its fuse blown. This is done in the same manner as permanently setting the other bitfields, as shown in figure 9.

Figure 7. Addressing mode enable pulse sequence

Figure 8. Pulse sequence to select addresses

Figure 9. Pulse sequence to encode lock bit

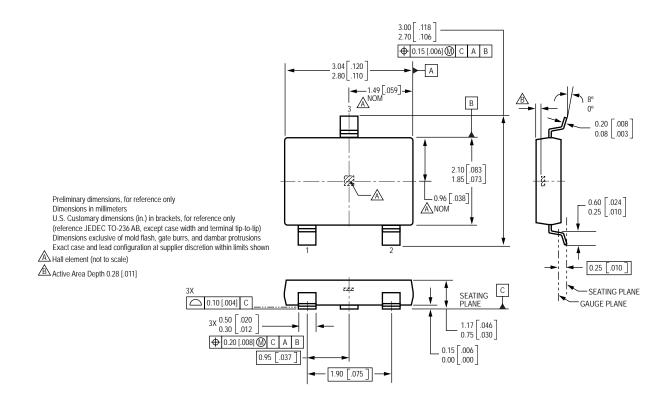

Package LH, 3-Pin (SOT-23W)

## **Pin-out Drawings**

Package LH, 3-pin SOT

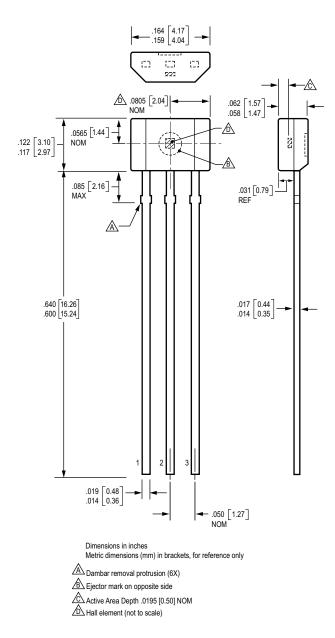

Package UA, 3-pin SIP

1. VCC 2. GND 3. GND

## Package UA, 3-Pin SIP

The products described herein are manufactured under one or more of the following U.S. patents: 5,045,920; 5,264,783; 5,442,283; 5,389,889; 5,581,179; 5,517,112; 5,619,137; 5,621,319; 5,650,719; 5,686,894; 5,694,038; 5,729,130; 5,917,320; and other patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro products are not authorized for use as critical components in life-support devices or systems without express written approval.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copyright © 2004, 2006 Allegro MicroSystems, Inc.